Điều chế độ rộng xung cho bộ nghịch lưu ba pha FPGA

1. GIỚI THIỆU

Điều chế độ rộng xung (PWM) bằng cách so sánh một tín hiệu tam giác có tần số cao với các tín hiệu điều chế ba pha đã được sử dụng rộng rãi cho các ứng dụng nghịch lưu ba pha, do sự đơn giản của nó. Tín hiệu điều chế được sử dụng sớm nhất là hàm sin ba pha ứng với phương pháp điều chế SPWM. Tuy nhiên, phương pháp này có vùng điều chế tuyến tính thấp. Phương pháp chèn tín hiệu hài bậc ba vào hàm sin ba pha để mở rộng vùng điều chế tuyến tính lên 15.5% so với SPWM đã được đề xuất và phát triển trong [1, 2]. Ưu điểm của những phương pháp điều chế này là thành phần sóng hài của dòng điện tải và tổn thất đóng cắt giảm đáng kể [3-4]. Do thực hiện dễ dàng, phương pháp điều chế SVPWM và DPWMMIN được sử dụng rộng rãi trong nhiều ứng dụng.

Việc sử dụng FPGA để thiết kế và thực hiện các bộ điều chế độ rộng xung cho các bộ nghịch lưu [5-7], đã xuất hiện rộng rãi và được coi là một giải pháp tối ưu cho chi phí [8]. So với bộ vi điều khiển và bộ xử lý tín hiệu số (DSP), FPGA có lợi thế hơn khi phần cứng có khả năng tái lập cấu hình, điều này tạo sự linh hoạt và rút ngắn thời gian thiết kế và điều chỉnh các sản phẩm. Hơn nữa, khả năng xử lý song song cho phép FPGA thực hiện các thuật toán nhanh hơn đáng kể. Do đó, thực hiện các phương pháp điều chế độ rộng xung trên FPGA có những thuận lợi như thiết kế phần cứng và phần mềm đơn giản và nhanh chóng, tần số đóng cắt cao, và bộ điều khiển có băng thông rộng hơn.

|

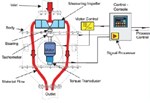

| Hình 1: Sơ đồ khối của bộ điều chế độ rộng xung cho bộ nghịch lưu ba pha |

2. NGUYÊN TẮC THIẾT KẾ

Hình 1 mô tả sơ đồ khối của bộ điều chế độ rộng xung cho bộ nghịch lưu ba pha với phương pháp điều chế: SVPWM và DPWMMIN; tần số đóng cắt fs = 20 kHz; thời gian trễ td = 0 ~ 6.4 s (bước hiệu chỉnh là 0.025 s). Bộ điều chế được thực hiện trên thuật toán số nguyên 10-bit. Nó bao gồm các mô - đun: bộ tạo tín hiệu tam giác, bộ tạo tín hiệu điều chế, bộ so sánh và bộ tạo thời gian trễ.

2.1 Bộ tạo tín hiệu tam giác

Bộ đếm 10 - bit và xung đồng hồ 40 MHz được sử dụng để tạo ra tín hiệu tam giác 20 kHz. Giá trị bộ đếm tăng dần từ - 500 đến 500 và sau đó giảm dần về - 500 trong một khoảng thời gian nhất định. Tần số của tín hiệụ tam giác được xác định bởi: , với fclk = 40 MHz là tần số xung đồng hồ và N = 500 là giá trị đỉnh của tín hiệu tam giác.

2.2 Bộ tạo tín hiệu điều chế

Mô-đun này nhận tín hiệu sin ba pha với biên độ và tần số nhất định tại ngõ vào để tạo ra các tín hiệu điều chế của phương pháp SVPWM và DPWMMIN. Hình 2 mô tả cấu trúc phần cứng của bộ tạo tín hiệu điều chế. Trong mô-đun, các thành phần hài bậc ba e được tính như sau e = - 0,5 (min + max) (SVPWM) và e = - N - min (DPWMMIN), trong đó min và max là mức nhỏ nhất và giá trị lớn nhất là tín hiệu sin ba pha ngõ vào.

|

| Hình 2: Cấu trúc phần cứng của bộ tạo tín hiệu điều chế |

2.3 Bộ so sánh

Trong mô-đun này, tín hiệu tam giác được so sánh với các tín hiệu điều chế để tạo các xung kích điều khiển các thiết bị đóng cắt bán dẫn.

2.4 Bộ tạo thời gian trễ

Do các thiết bị đóng cắt bán dẫn không lý tưởng, tác động đóng cắt của chúng có một độ trễ nhất định tương ứng với tín hiệu xung kích. Để tránh sự trùng dẫn của các cặp công tắc trong cùng một nhánh làm ngắn mạch nguồn DC, thời gian trễ được chèn vào tại cạnh lên của xung kích điều khiển trong bộ tạo thời gian trễ. Thời gian trễ có thể điều chỉnh từ 0 đến 6.4ms với bước hiệu chỉnh là 0.025 ms.

3. KẾT QUẢ THỰC NGHIỆM

Bộ điều chế độ rộng xung được thiết kế và thực hiện trên FPGA A2F500M3F của SmartFusion. Nó được thiết kế chỉ sử dụng 5% tài nguyên phần cứng của FPGA. Điều này chứng tỏ sự phù hợp của nó để kết hợp với các chức năng điều khiển khác trong các ứng dụng của bộ nghịch lưu ba pha.

|  |

| (a) SVPWM, | (b) DPWMMIN |

Hình 3: Dạng sóng ngõ ra vao, vbo, vco qua bộ lọc:

Ngõ ra của bộ nghich lưu được nối với tải RL để kiểm tra hiệu quả điều chế. Thông số hệ thống như sau R = 5 Ω, L = 0.8 mH and Vdc = 18 V. Trong Hình 3, có thể thấy rằng dạng sóng ngõ ra vao, vbo, vco qua bộ lọc giống như dạng sóng của là tín hiệu hài bậc ba e và có tần số gấp ba lần tần số cơ bản của điện áp dây đầu ra. Các kết quả thực nghiệm là phù hợp với lý thuyết. Hình 4 mô tả quỹ tích dòng điện ba pha của các phương pháp điều chế. Kết quả thực nghiệm cho thấy rằng bộ điều chế có thể tạo ra điện áp ngõ ra mong muốn với dải tần điều khiển rộng. Mặc dù yêu cầu tần số cơ bản đầu ra là rất cao tại 1 kHz, nhưng quỹ tích dòng điện ba pha vẫn là hình tròn, một yếu tố quan trọng để đánh giá hiệu quả của bộ điều chế.

|  |

| (a) SVPWM | (b) DPWMMIN |

Hình 4: Quỹ đạo dòng điện ba pha:

4. KẾT LUẬN

Trong bài này, bộ điều chế độ rộng xung đã được thiết kế thành công trên FPGA và có khả năng thực hiện hai phương pháp điều chế SVPWM và DPWMMIN. Nó chỉ chiếm một phần nhỏ tài nguyên của FPGA nên nó có thể tích hợp vào hệ thống điều khiển vòng kín để đạt được một giải pháp toàn diện cho truyền động AC. Kết quả thực nghiệm đã chứng minh tính hiệu quả của bộ điều chế và phù hợp với lý thuyết. Ngoài ra, bộ điều chế tạo ra điện áp mong muốn với dải tần số điều khiển rộng

Gần đây nhất

Bản quyền © 2015 ngananhphat.com.vn|Designed by viễn nam